Extreme Ultraviolet lithography, widely referred to as EUV lithography, stands as the pivotal manufacturing method driving the advancement of semiconductor process nodes below 7 nanometers. Harnessing 13.5 nanometer wavelength light, this approach enables chip manufacturers to create exceptionally compact and intricate circuit designs that earlier deep ultraviolet methods could not deliver economically or physically. As the semiconductor sector advances toward 3 nanometers, 2 nanometers, and even smaller scales, EUV lithography continues to evolve at a rapid pace to address extraordinary technical and financial challenges.

From First-Generation EUV to High-Volume Manufacturing

Early EUV systems functioned mainly as research platforms, restricted by weak light source output, short operational cycles, and intricate mask management, while over the last decade EUV has evolved into a robust high-volume manufacturing technology adopted by leading foundries and integrated device manufacturers, with current EUV scanners delivering production-grade reliability capable of processing thousands of wafers per day.

Key improvements that enabled this transition include:

- EUV source power has risen substantially, evolving from under 50 watts in the earliest equipment to surpassing 250 watts in modern production machines

- Collector mirrors have been refined to channel EUV photons toward the wafer with greater efficiency

- Enhanced vacuum infrastructures minimize EUV light absorption by eliminating air interference

- More advanced photoresists have been formulated to perform optimally at EUV wavelengths

These advances allowed EUV to replace complex multi-patterning steps used in older lithography, significantly reducing process complexity and defect risk.

Single-Exposure Patterning and Reduced Complexity

EUV lithography’s most notable benefit lies in its capacity to achieve single‑exposure patterning for features that once depended on double or even quadruple patterning, and at the 7‑nanometer node and smaller, deep ultraviolet lithography relied on several precisely aligned exposures, which drove up costs, prolonged cycle times, and increased the risk of yield loss.

EUV simplifies manufacturing by:

- Reducing the number of masks per layer

- Lowering overlay error between patterns

- Shortening overall process flows

- Improving pattern fidelity for dense logic structures

This streamlining becomes crucial as process nodes become smaller, since even tiny misalignments may trigger functional breakdowns at near‑atomic scales.

High Numerical Aperture EUV and the route forward past the 2-nanometer frontier

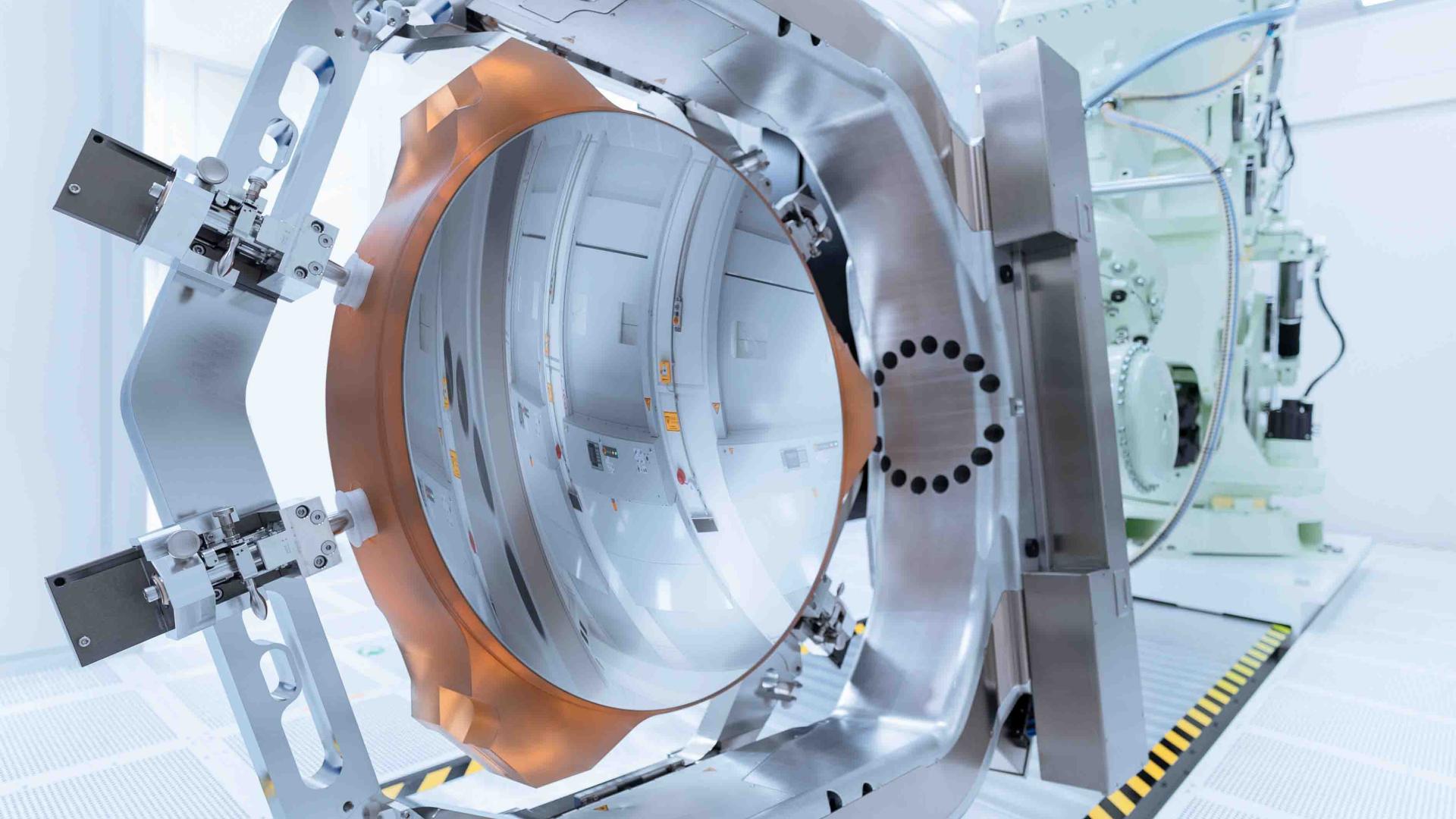

As standard EUV approaches its resolution limits, the industry is introducing High Numerical Aperture EUV, often referred to as High-NA EUV. Numerical aperture determines how finely a lithography system can focus light, and increasing it directly improves resolution.

High-NA EUV systems increase numerical aperture from 0.33 to approximately 0.55, enabling:

- Smaller minimum feature sizes without excessive pattern splitting

- Improved edge placement accuracy

- Better scaling of critical layers such as gate and metal interconnects

These systems are physically larger and more complex, requiring new optical designs, tighter vibration control, and redesigned fabs. However, they are essential for enabling process nodes at 2 nanometers and smaller while maintaining economically viable yields.

Advances in EUV Photoresists and Materials

Photoresists play a decisive role in how effectively EUV patterns can be transferred onto silicon. Traditional chemically amplified resists struggle with the tradeoff between resolution, line edge roughness, and sensitivity at EUV wavelengths.

To address this, material suppliers are developing:

- Metal-oxide-based resists engineered for enhanced absorption performance

- Refined chemically amplified resists designed to minimize stochastic irregularities

- Innovative underlayer materials formulated to boost pattern definition

Minimizing stochastic phenomena, including unpredictable micro-bridges or fractures, becomes crucial at advanced nodes, since even one defect may influence transistor performance or overall yield.

Advances in Mask Technology and Defect Management

EUV masks differ drastically from conventional photomasks, using reflective multilayer stacks rather than transparent glass, and their extreme defect sensitivity means even minor flaws may be transferred straight onto wafers.

Recent innovations include:

- Refined multilayer coating methods designed to minimize inherent defects

- State-of-the-art actinic inspection systems that evaluate masks through EUV illumination

- Pellicles that shield masks while staying transparent to EUV exposure

Pellicle technology has posed considerable difficulties, as it demands extremely thin materials that can also withstand intense EUV power, yet advances in this field have markedly extended mask service life and enhanced overall yield consistency.

Computational Lithography and Design Co-Optimization

EUV lithography’s progression extends beyond hardware, as computational lithography and design technology co-optimization grow ever more vital for advancing to smaller nodes. Sophisticated algorithms are used to model the interaction of EUV light with masks, resists, and the wafer’s surface profile.

These tools make it possible to:

- Optimized mask patterns that compensate for optical distortions

- Design rules tailored specifically for EUV capabilities

- Early detection of manufacturability risks during chip design

By aligning design and manufacturing constraints, chipmakers can extract maximum value from EUV systems while minimizing costly redesign cycles.

Strategic and Economic Influence on the Semiconductor Sector

EUV lithography systems stand among the costliest manufacturing instruments ever created, with each scanner priced at well over one hundred million dollars, yet their high expense is offset by the economic value they deliver by cutting overall process steps and allowing far greater transistor density per wafer.

EUV has become a strategic technology, influencing:

- Global rivalry within cutting-edge logic production

- Long-range capital deployment plans pursued by foundries

- Supply chain reliance on optical systems, specialized materials, and high-precision components

Gaining access to cutting-edge EUV equipment is increasingly becoming the factor that determines which companies can stay competitive at the forefront of semiconductor technology.

A Wider Look at the Continuing Progress of EUV

EUV lithography is no longer a single breakthrough but an evolving ecosystem of optics, materials, computation, and manufacturing discipline. Each generation of EUV improvements extends the practical limits of Moore’s Law while reshaping how chips are designed and built. As High-NA EUV, advanced resists, and tighter design integration converge, the technology continues to unlock smaller process nodes not by one dramatic leap, but through sustained, coordinated innovation across the entire semiconductor value chain.